景嘉微JH920芯片板卡設計(jì)

發布時間:2025-10-06 08:35:35

|

類別 |

景嘉微(wēi)JH920芯(xīn)片板卡設計

|

|

產品所(suǒ)屬行業 |

通信板卡 |

|

主要芯片 |

|

|

單板類(lèi)型 |

金手指板卡 |

|

Pin數 |

4780 |

|

層數 |

10 |

|

最高信號速率 |

16Gbps |

|

難點 |

1. 該產品中內存設計主要有2個 GDDR6-1000MHz內存(cún)芯片,因此在GDDR6內存的信(xìn)號設(shè)計上必(bì)須滿(mǎn)足GDDR6的(de)內存布線標準, Via stub 小於 40mil,信號布在靠近(jìn)芯片的最鄰近層 2. GPU內電(diàn)源種類比較多,大小(xiǎo)電源將近(jìn)30多個,其中(zhōng)1A以上電源有10多個,PLL小電源將近20多個,GPU CORE電源最大電流70A, GDDR6電源最大10A

|

|

其他 |

主要信號介紹:

PCIE總線遵從PCIE4.0規範,單對差分線速率支持16Gbps HDMI高速(sù)總線單對差分速(sù)率可達594MHz千兆網口信號:PHY芯片的RX和TX信號 eDP高速總線單對差分速率可達5.4Gbps GDDR6-1000MHz內存芯片,各自組成1個16位的GDDR內存條(tiáo)。 因此(cǐ)在GDDR6內存(cún)的信號設計上必須滿(mǎn)足GDDR6的內存布線標準

|

|

我司對(duì)策 |

1. GDDR6阻抗設計 :單端:40 歐 差分:80 歐 REF CLK/PLLTEST 差分:100 歐 間距要求:

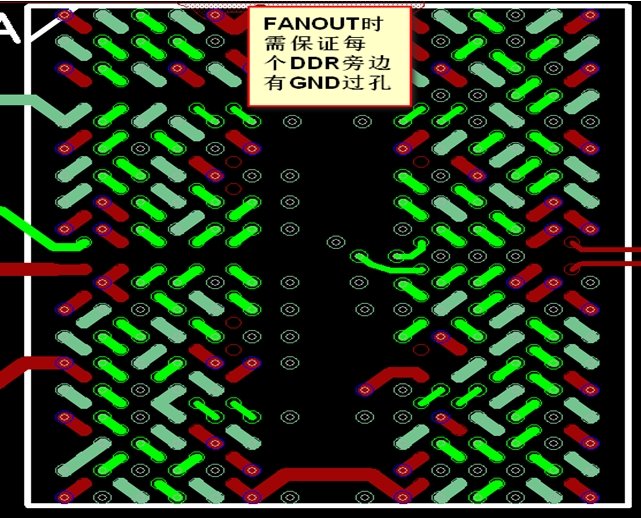

2. 每個信號必需有 gndvia,gndvia到信號的距(jù)離最大不超過 1mm。 DRAM顆粒球Pitch為0.75mm,信號扇出(chū)采(cǎi)用dogbone ,拉開信號之間過孔的距離,減少串擾。

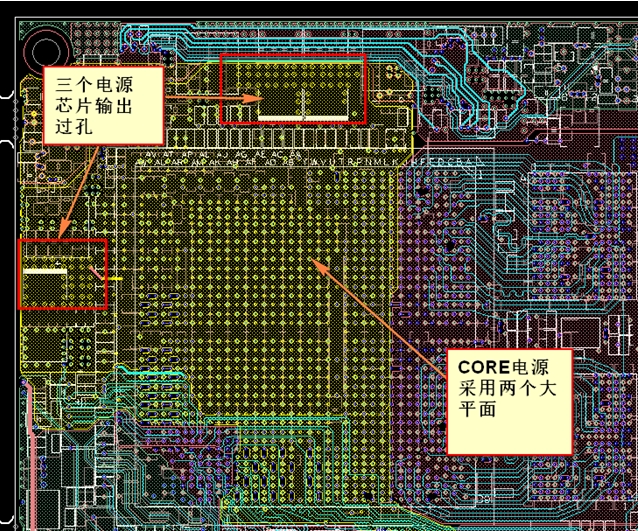

3. CORE電源最大電流70A,每個PIN腳都要保證有0402的濾波電容(róng),為了保證載流,優先考慮用兩個1OZ的平麵給其一個(gè)完整的(de)平麵

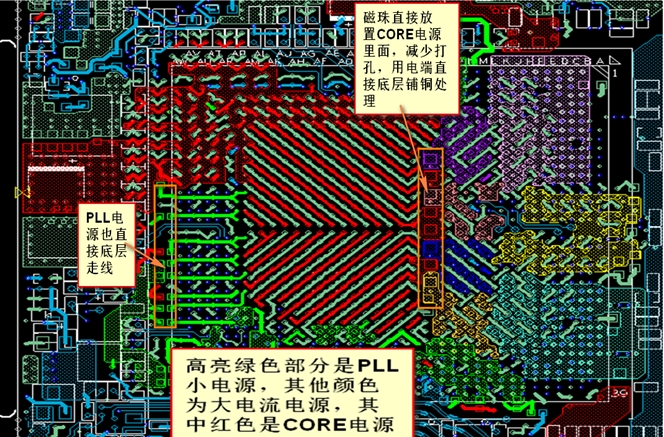

4. 其他小電源采用能不打孔盡量不打孔(kǒng),采用磁(cí)珠直接供電,PLL電源也直接底層走線,這樣可以減少打孔空間,還能保證經過每一個濾波電容到PIN腳,濾波效果更好

香蕉视频污视频科技在海(hǎi)內外設立二十餘個研發機構,全球高速PCB設計工程(chéng)師800餘人,每年15000多款PCB設計經驗,就近(jìn)服務,便於溝通。#PCB設計#香蕉视频污视频(bó)#香蕉视频污视频PCB設計#PCB設計案例#一(yī)站(zhàn)式服務

|